Well, I bet nobody comes on that blog still.

But anyway I am going to publish the results of my work.

I have complete what I think is a good beginning of the Snes PPU chip.

It has all the logic/structure for everything except sprites.

Of course, some inner part are still untested but structure is inside and timing is thought at least.

Now what been proven work on my FPGA board.

- BG 1/2/3/4 memory access for all graphic mode done.

- Of course support for various bitmap format of each mode.

- Support of tile flip 8/16 pixels.

- Support of map of 32/64 tiles mode.

Out of three bugs I was looking for, two were related to SPEC miss.

(Document are not accurate in two places)

My own bug were :

- I had to disable the register writing side of the PPU that went berserk and destroyed the test data.

- I use a modified version of Snes9x with a custom DLL to trap all the call to the registers and dump memory into VHDL tables to be able to take a "screenshot" of the graphics chip state and compile it in my design to verify if the chip does the rendering correctly.

(Big-mega-thanks to ThunderZ for the support, and also future BSnes patching, being too much busy with other stuff)

My DLL for-loop that was dumping the table had A BUG. I lost two weeks because of a LOOP in C++ where like 4000 lines of VHDL CODE WAS CORRECT RIGHT AWAY WITHOUT ANY SIMULATOR !!! Shit... gotta kick my ass sometime.

What remains soon :

- Mode7 need to be finished.

- Mosaic is half-baked.

- Verify and debug window / main-sub variation.

What remains later :

- HiRes

- Interlace (need to check what that means... the chip already actually work at double resolution)

- Sprites

Here's some pix for the curious :

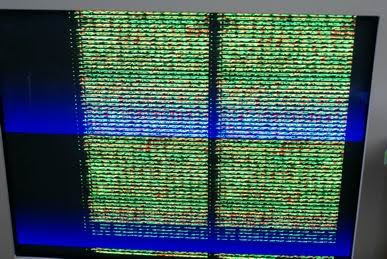

Trying to debug... GARBAGE. Divided the screen in 32 pixel height block and value reflected internal register value.

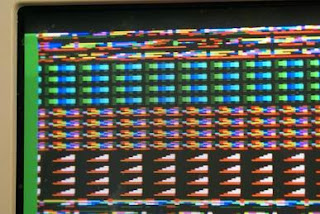

After finding that I was reading garbage and that my register logic cpu-side was going berserk and I fixed it, I started to have something like that after a few hours of debug.

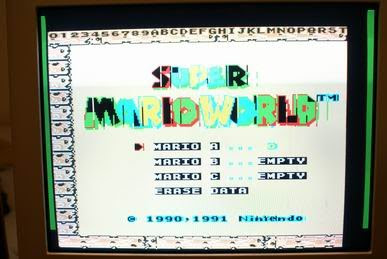

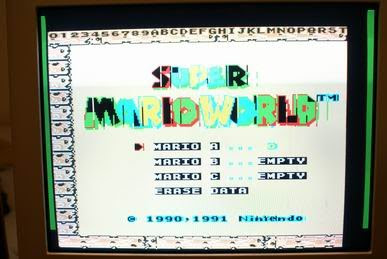

And after a whole week-end, it gives something like that.

Still my main-sub unit not beeing ready, I hard coded the priority just to display the 3 BGs correctly.